工程目标

基于TLFM20S-EVM开发板,搭建PS和PL联合开发的基础功能,使用PS侧的CPU通过EMIO控制PL侧的LED灯闪烁,同时实现PS和PL独立调试(即JTAG独立模式,通过EMIO引出PJTAG)。

开发环境

- PL开发工具:VIVADO 2018.3,主要用于PL侧逻辑开发和使用XILINX丰富的IP资源(若无需复杂的IP资源,则可以单独使用PROCISE)。

- PS开发工具:IAR 8.11.2.13606,用于编写PS侧的C语言

- 转换工具:PROCISE 2024.1.1,用于转换VIVADO工程,生成相应的BSP供后续PS开发。

- 开发板:TLFM20S-EVM,核心芯片为复旦微的FMQL20S400M,对标XILINX的XC7Z020CLG400-2。

- 下载器:XILINX的JTAG下载器、JLINK仿真器。

工程搭建步骤

软件开发环境配置这里不再叙述,下面详细介绍工程搭建的步骤。

-

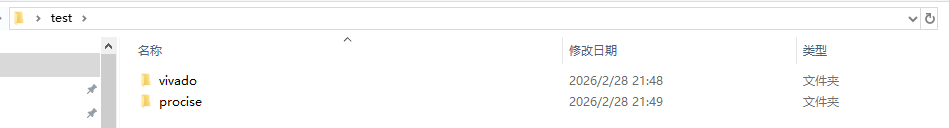

新建工程文件夹,如test。然后新建vivado和procise两个子文件,分别存放后续的vivado工程文件和procise工程文件(IAR相关代码默认存放在procise工程文件夹中,无需新建)。

-

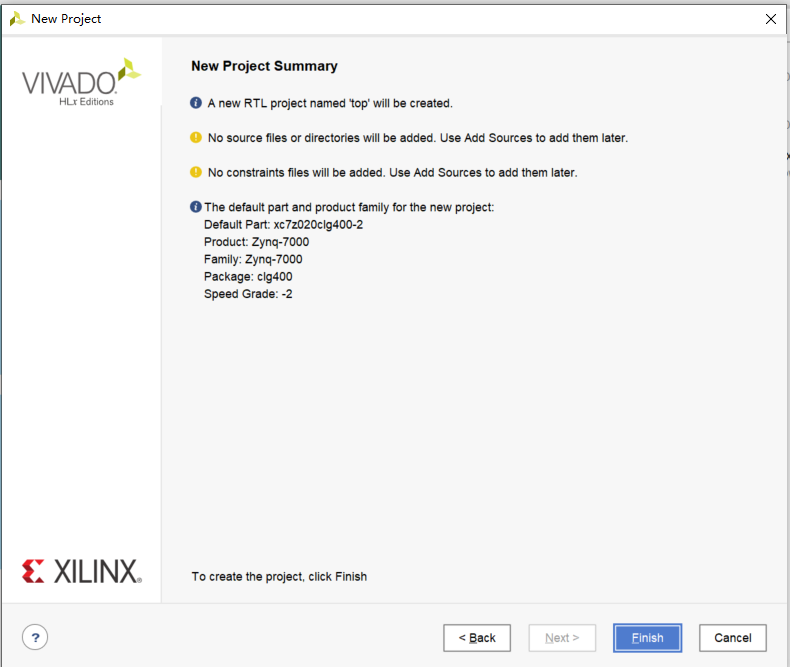

新建VIVADO工程。工程名称设置为top,存放在上一步新建的test\vivado文件夹中。后续目标芯片选择XC7Z020CLG400-2。最后完成VIVADO工程的建立。

-

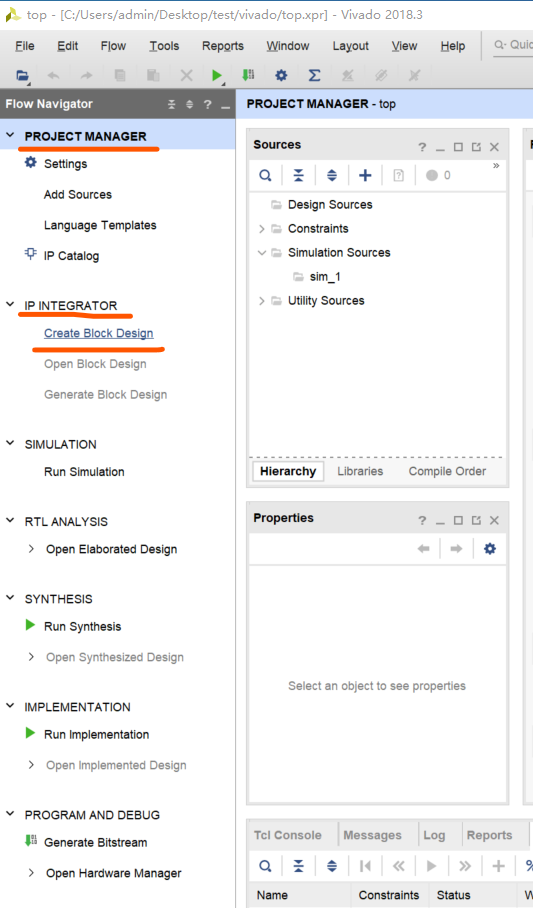

左侧Flow Navigator中选择IP INTEGRATOR->Create Block Design。

-

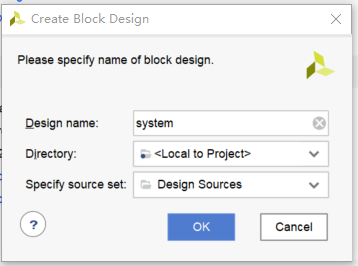

弹出Create Block Design对话框,Design name设置为system。其余默认即可。

-

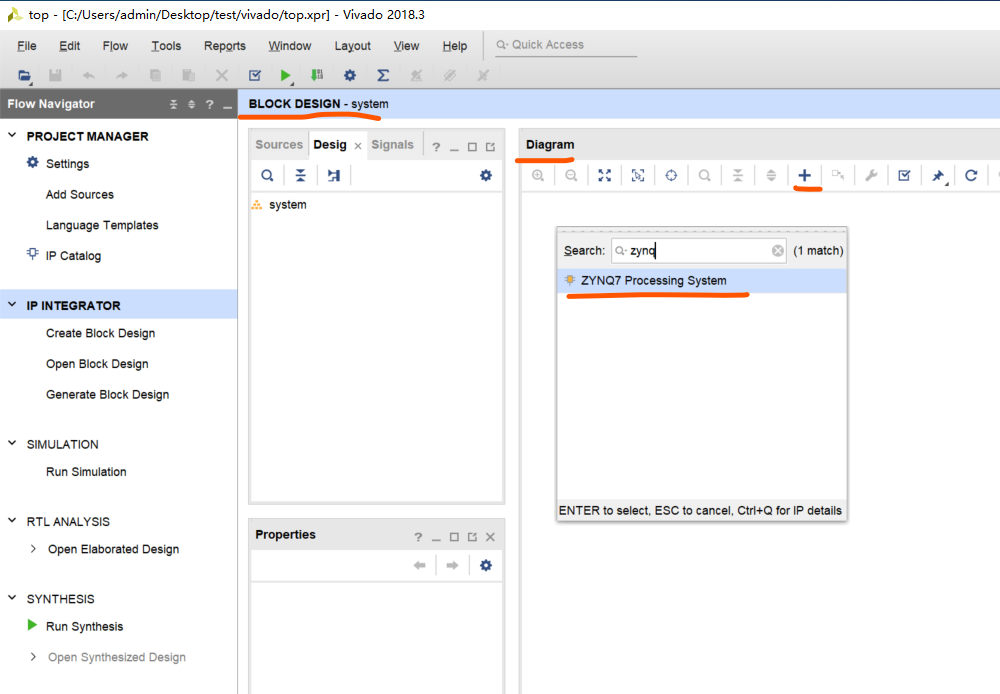

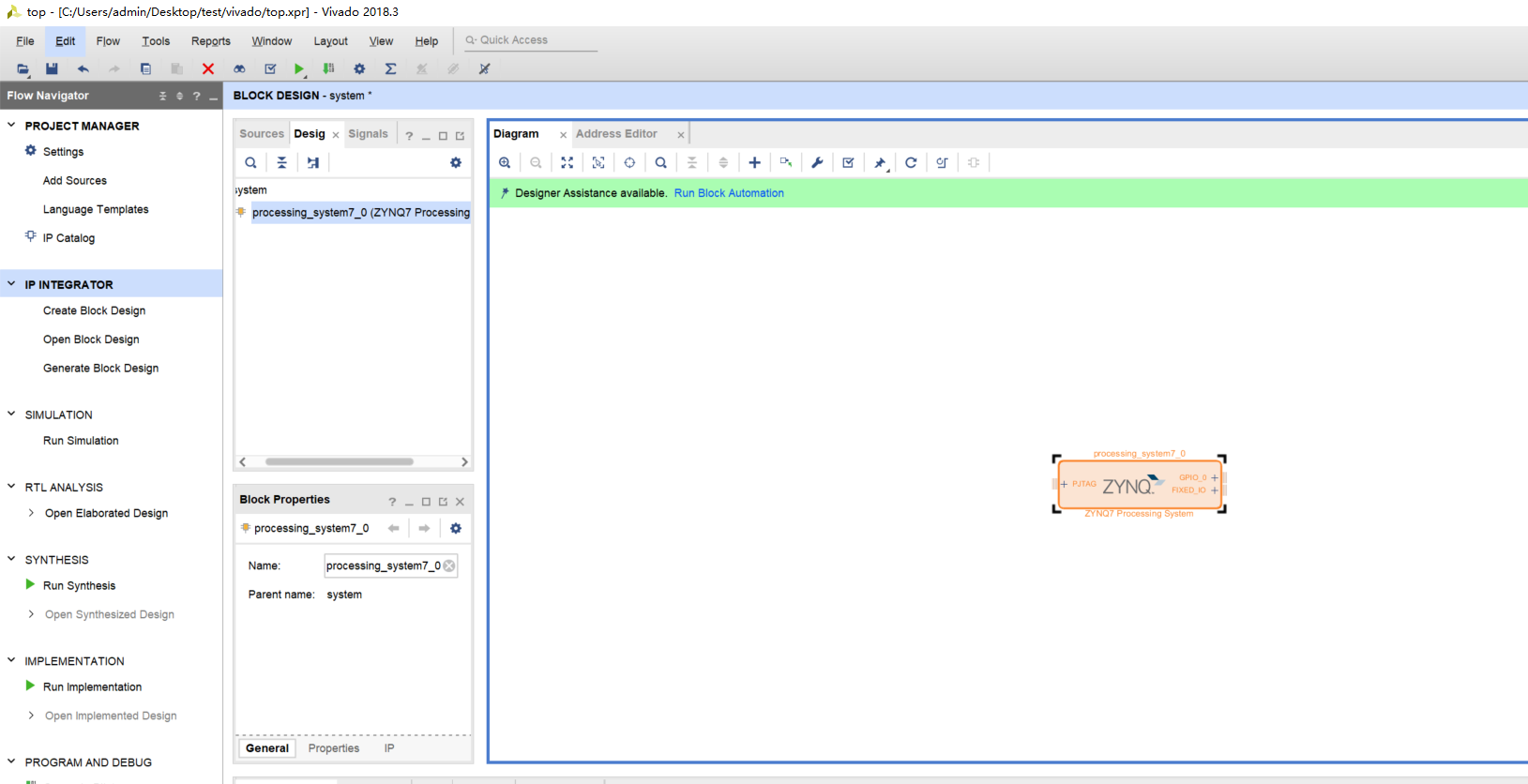

在Block Design区域中,找到Diagram区域,单击+,搜索ZYNQ7 Processing System,双击添加。

-

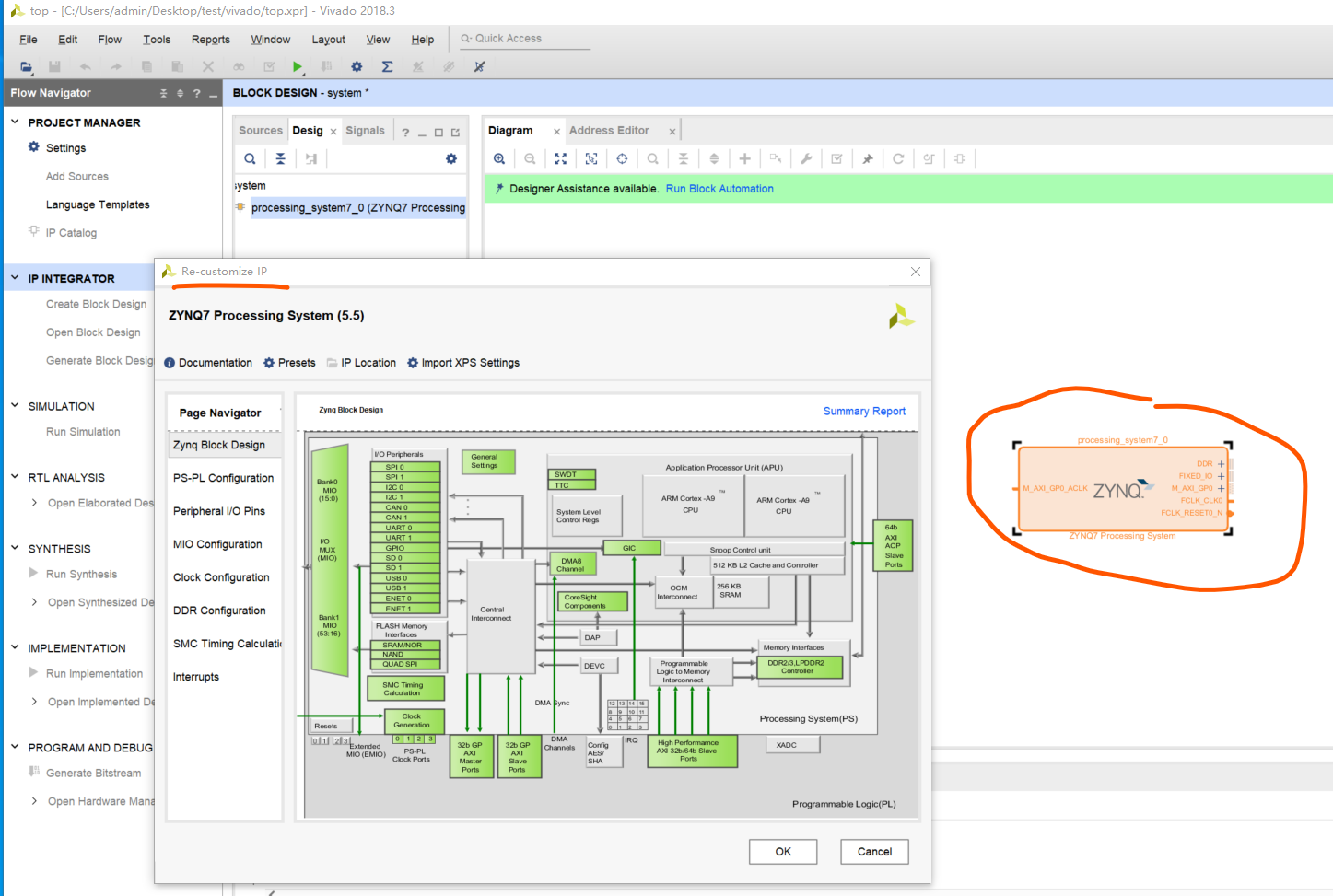

双击已添加到Diagram区域的processing_system7_0,打开Re-customize IP对话框。

-

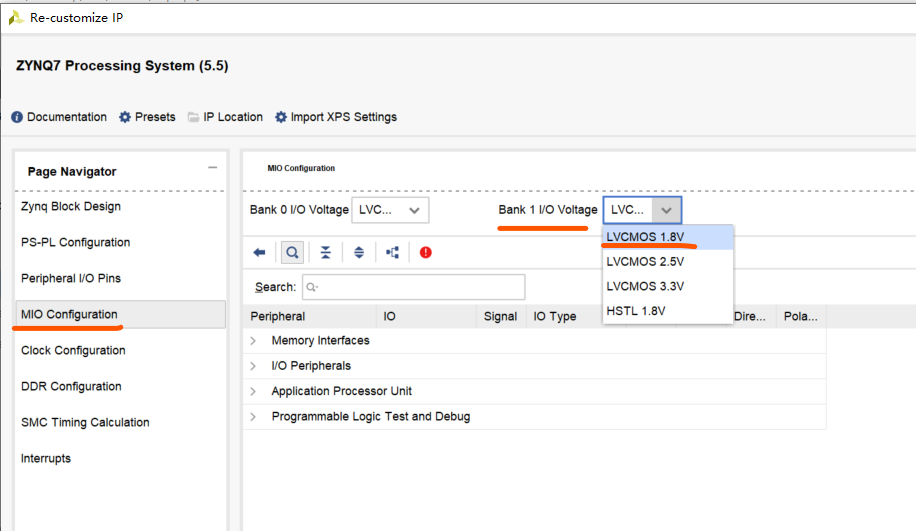

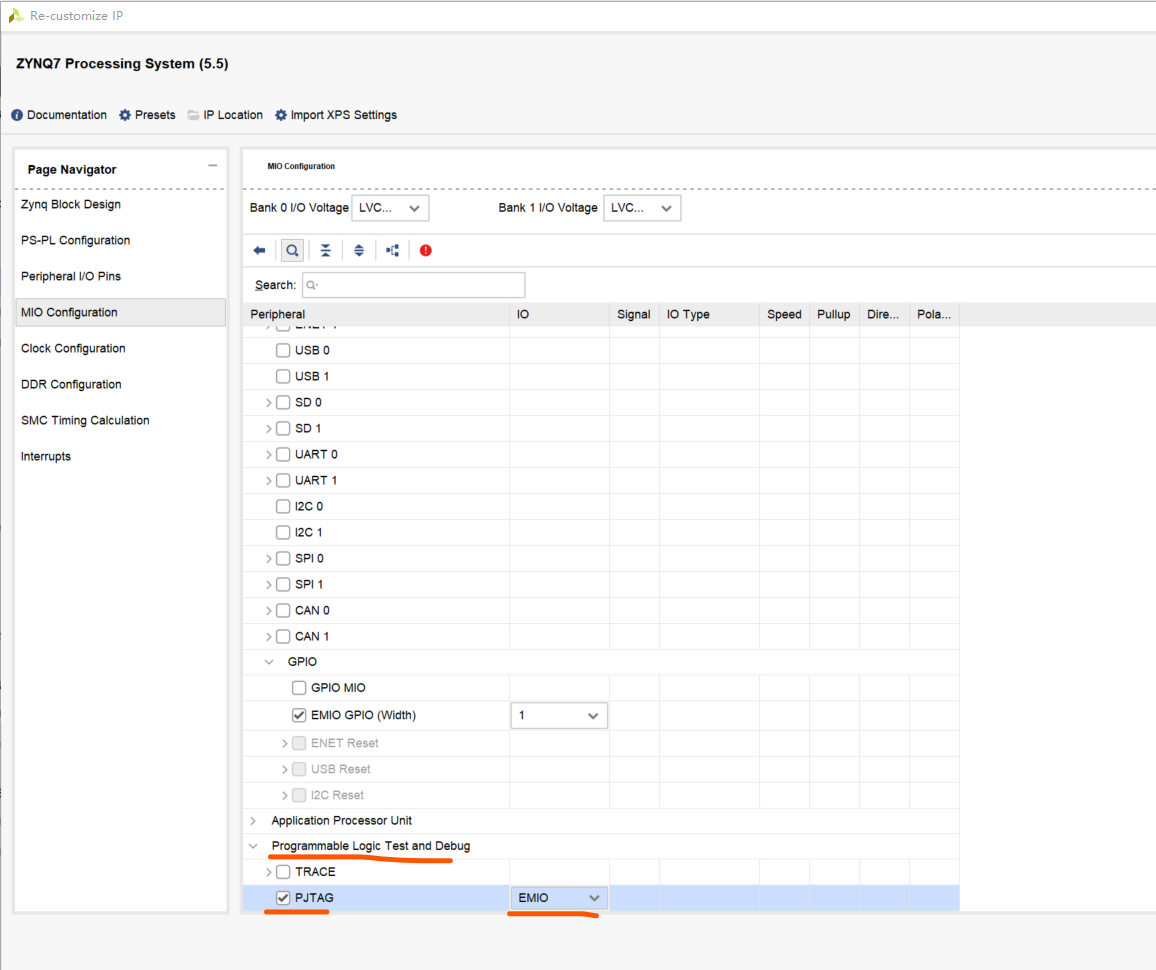

首先配置EMIO。Page Navigator中选择MIO Configuration,BANK1 I/O Voltage选择LVCMOS 1.8V。

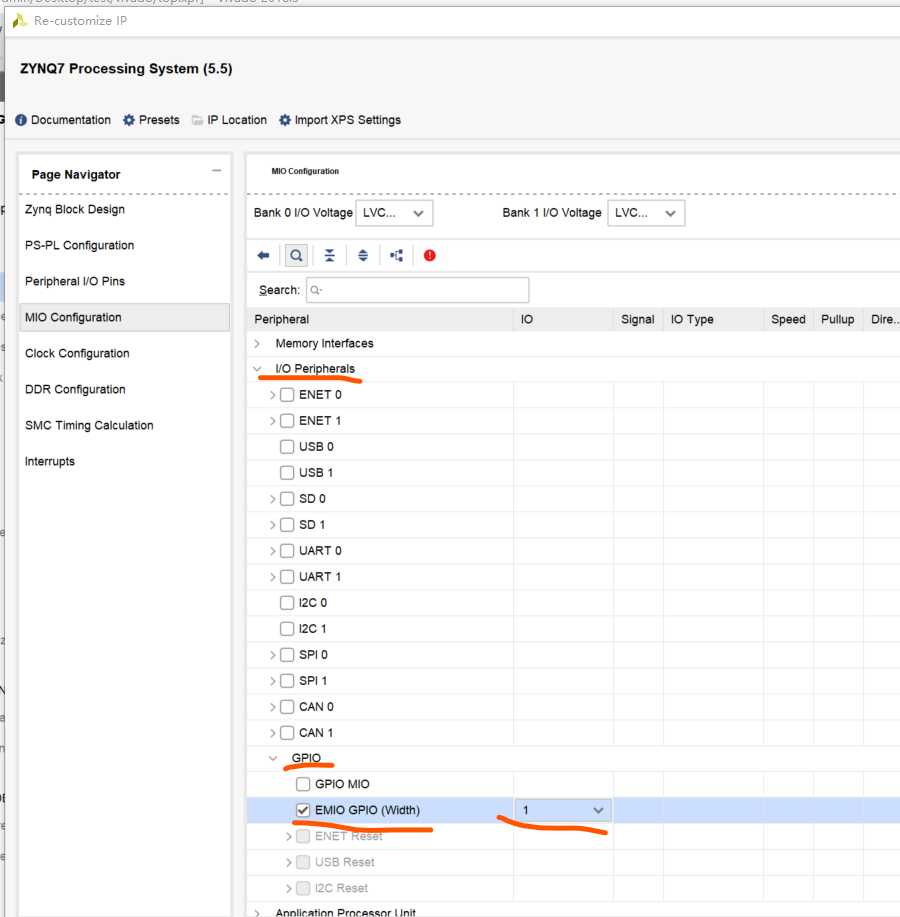

I/O Peripherals中选择GPIO,勾选EMIO GPIO,配置位宽为1。

选择Programmable Logic Test and Debug,勾选PJTAG,配置为EMIO。

-

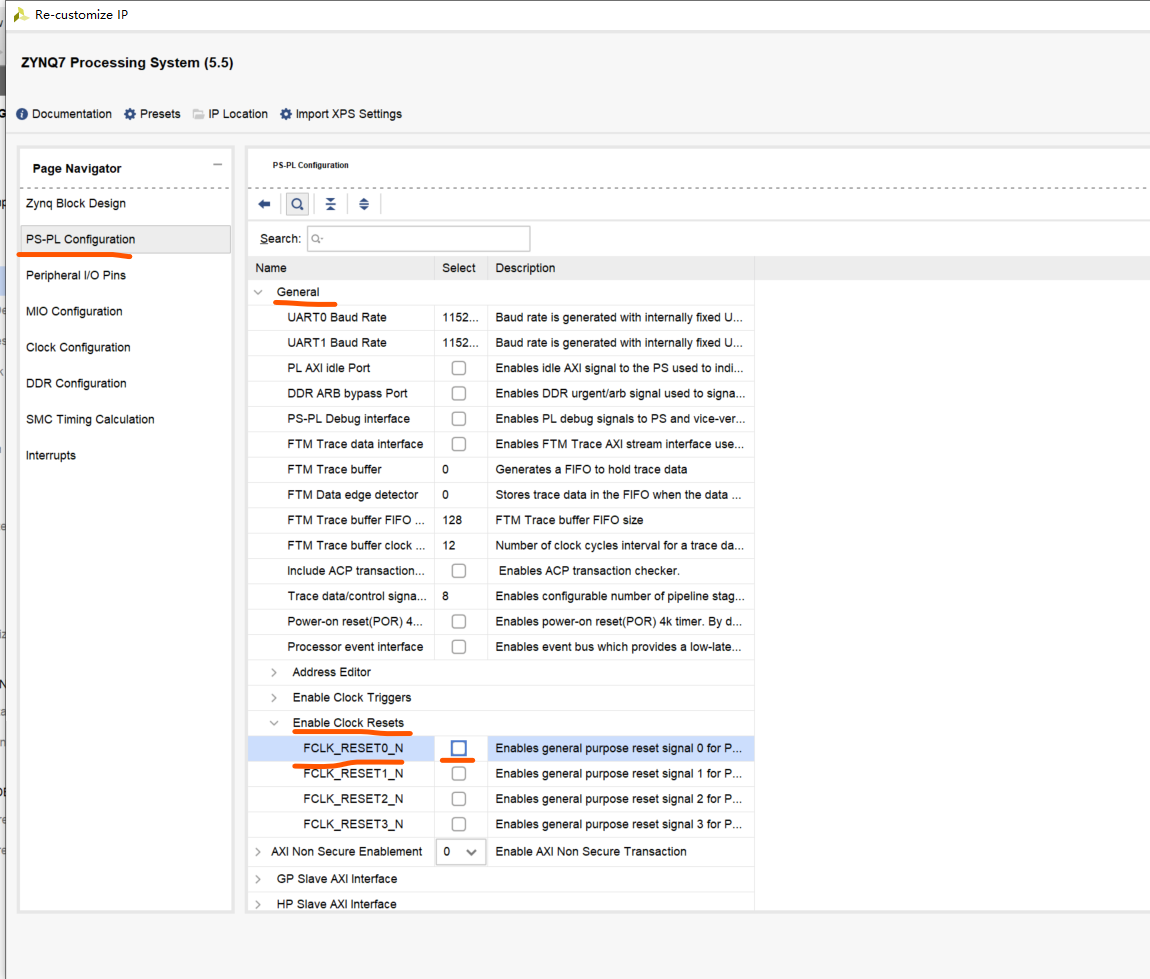

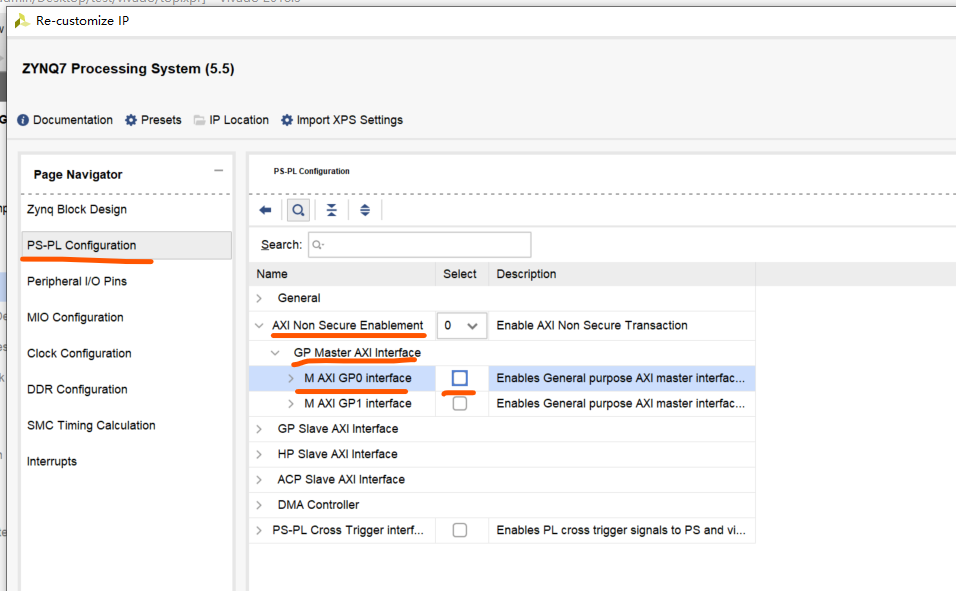

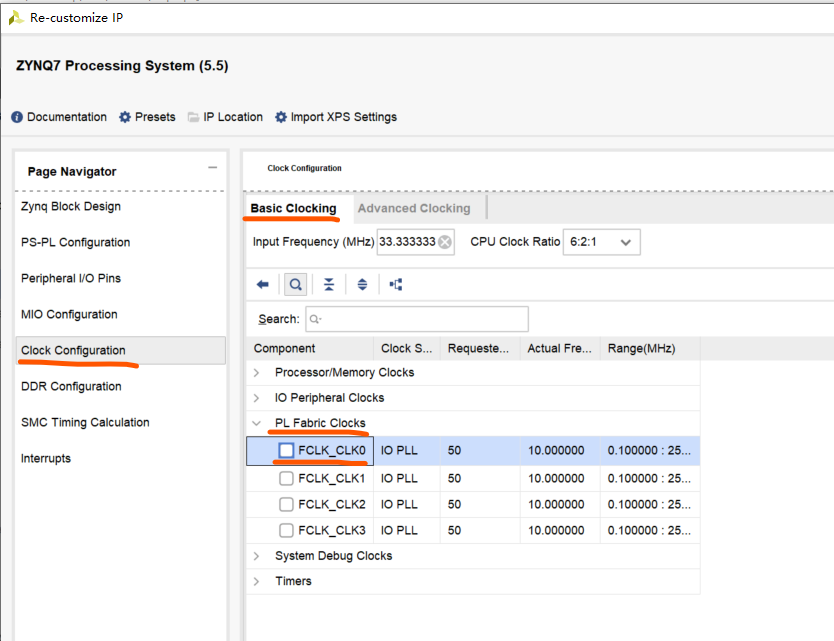

下面删除无需使用的配置,使最后CPU的配置清爽、简单明了。

PS-PL Configuration -> General -> Enable Clock Resets,取消FCLK_RESET0_N的勾选。

PS-PL Configuration -> AXI Non Secure Enablement -> GP Master AXI Interface,取消M AXI GP0 Interface的勾选。

Clock Configuration -> Basic Clocking -> PL Fabric Clocks,取消FCLK_CLK0的勾选。

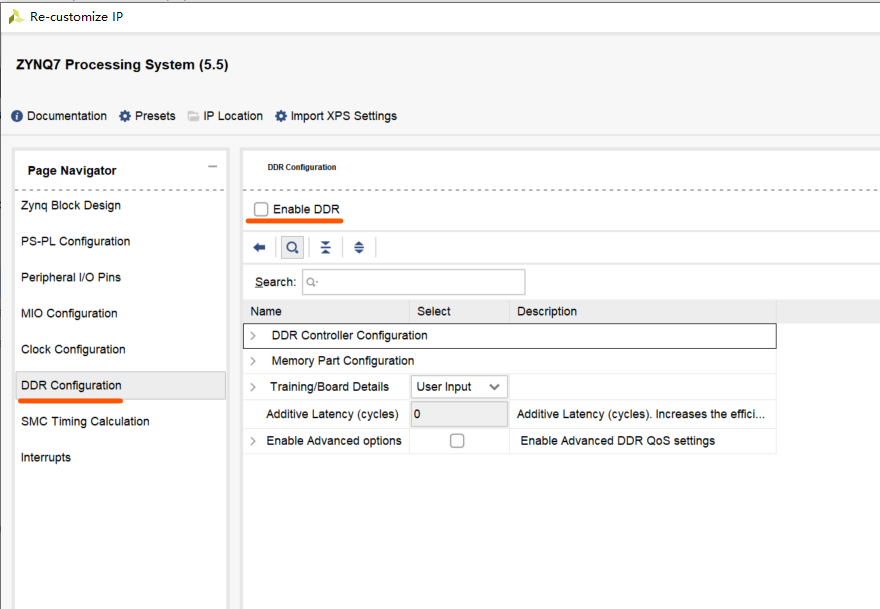

DDR Configuration中取消Enable DDR的勾选。

-

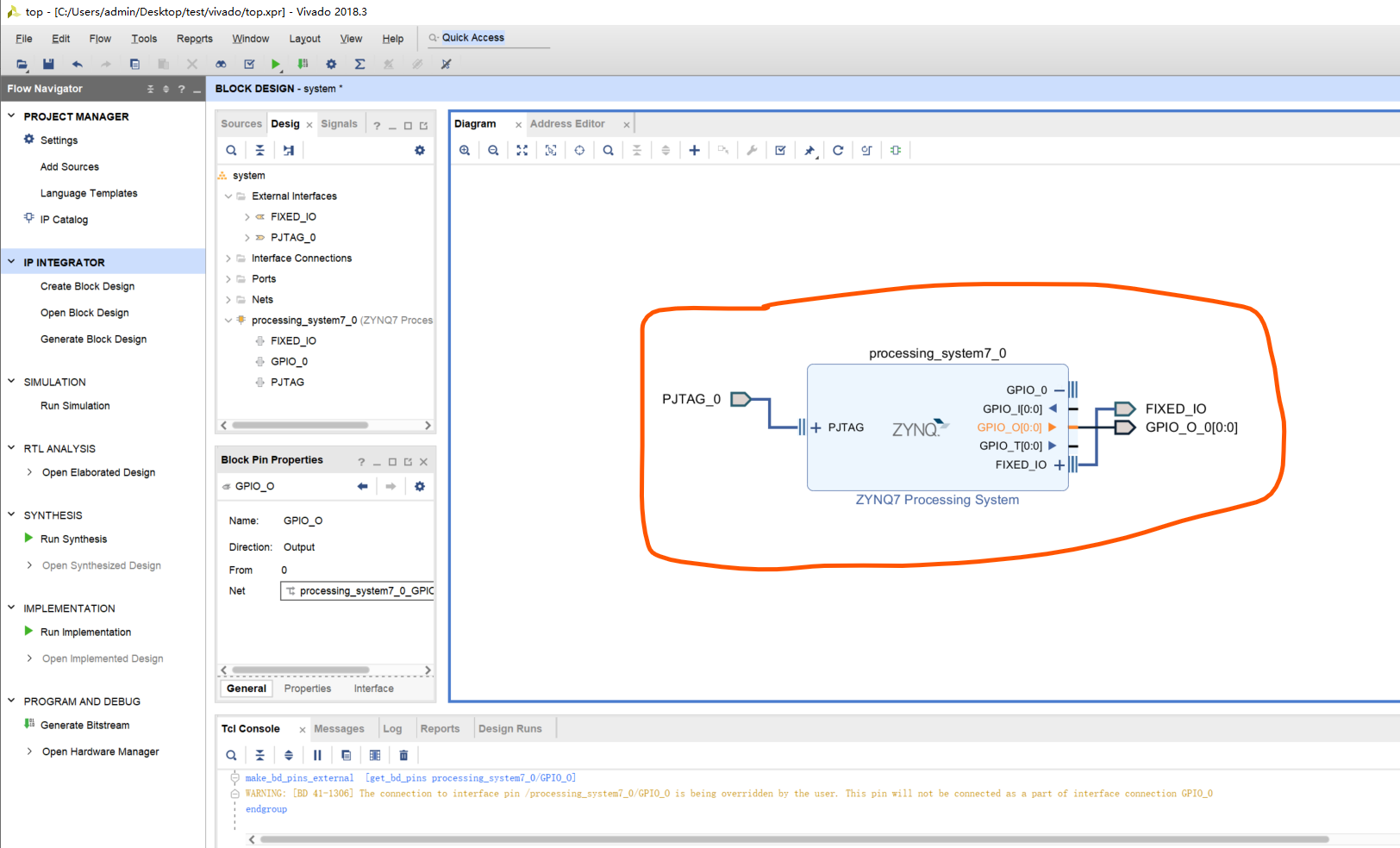

单击OK,得到最终的CPU IP如下图。

-

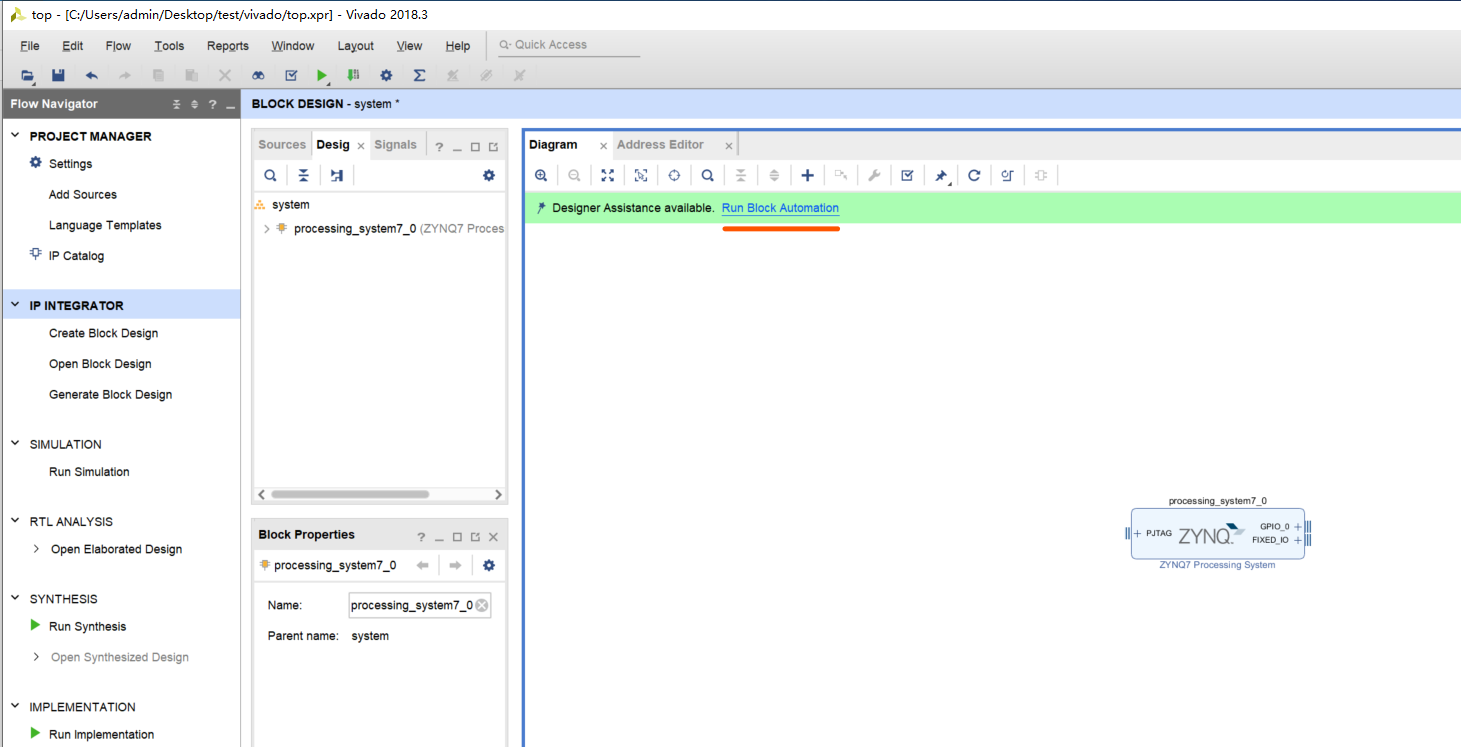

单击上方的Run Block Automation,自动将CPU的专用管脚引出。

引出后的效果如下图所示。

-

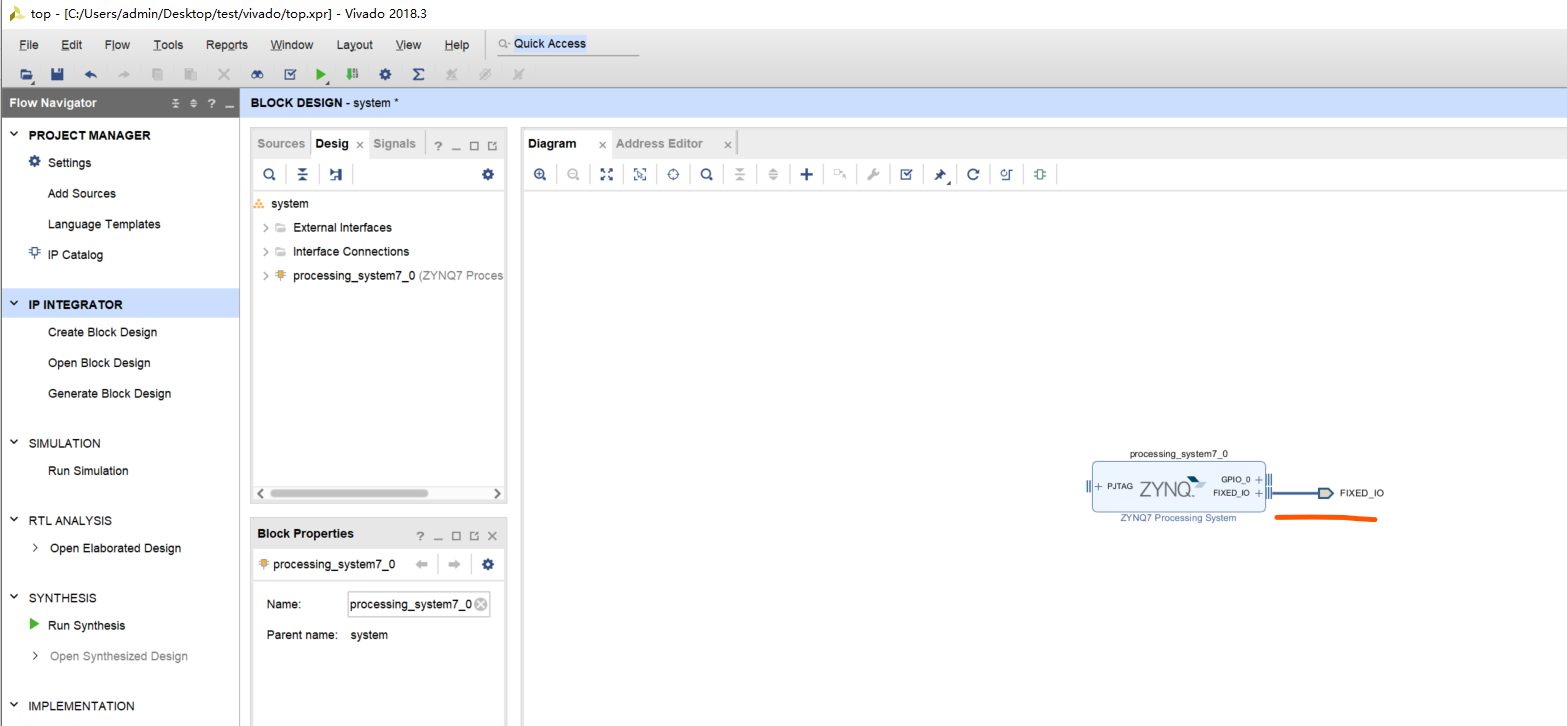

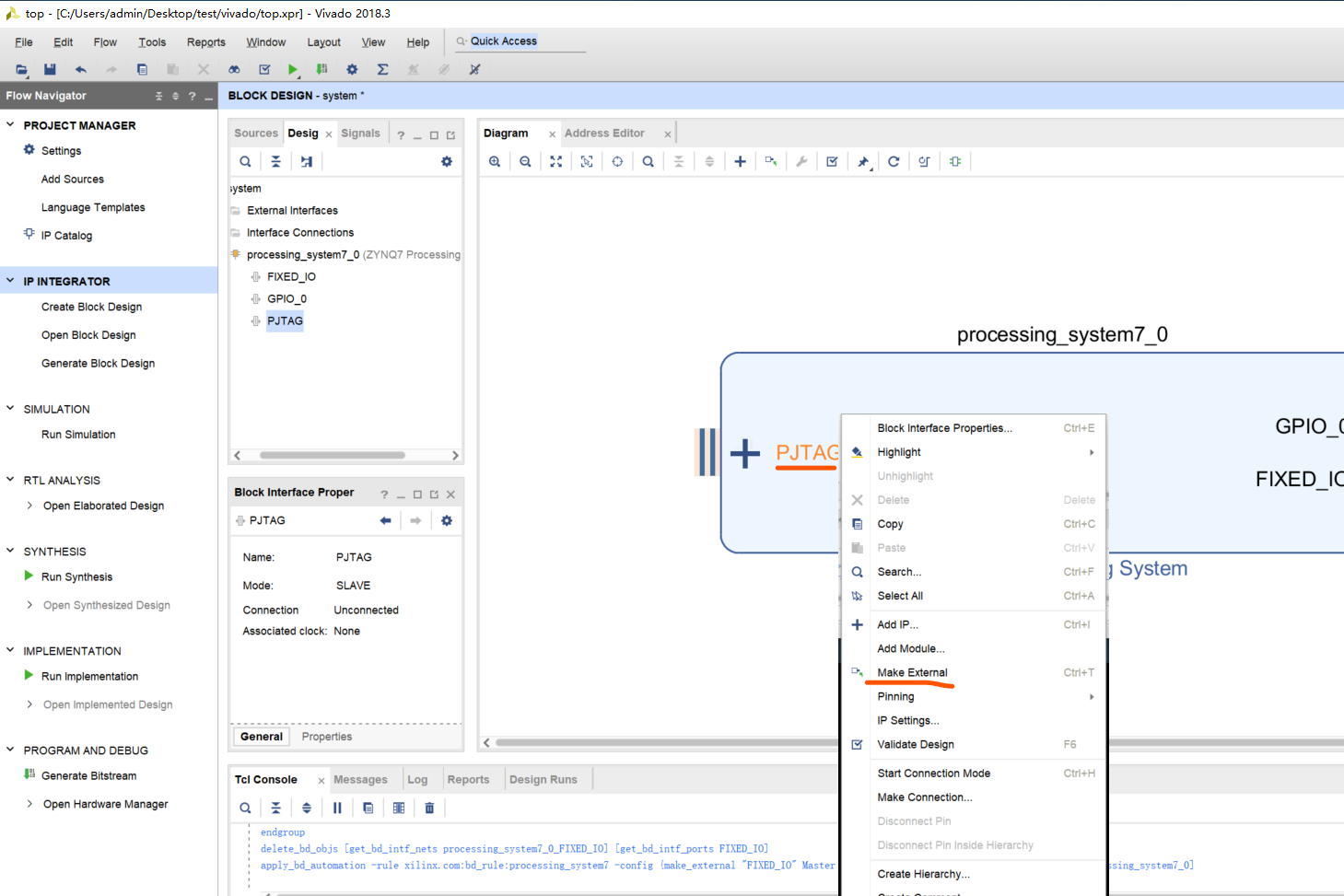

下面依次引出自定义的PJTAG和GPIO_0管脚。

首先引出PJTAG管脚。单击processing_system7_0中的PJTAG管脚,右击选择Make External。

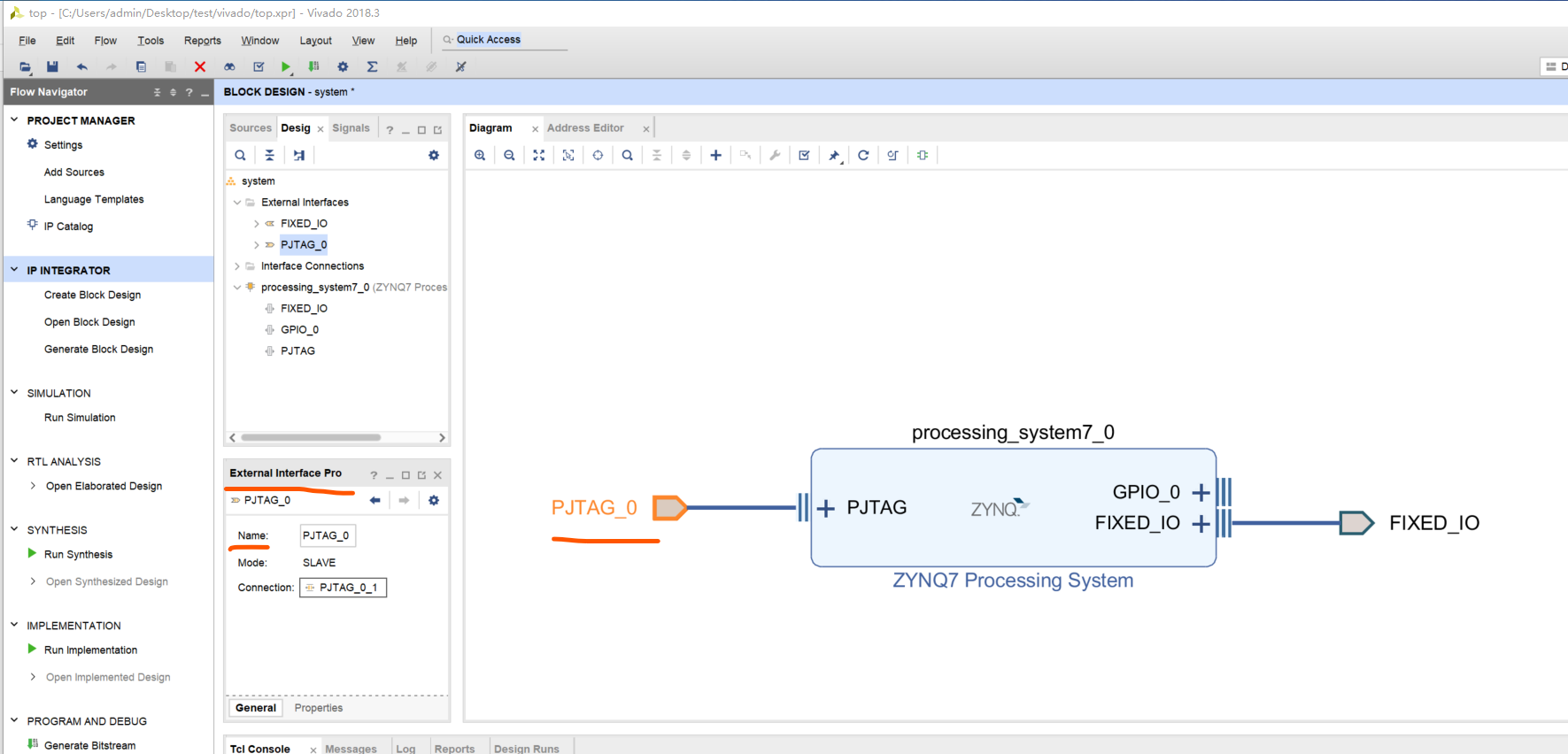

可以看到自动引出PJTAG_0管脚。若需要修改PJTAG_0名称,可选择PJTAG_0,在左侧的External Interface Pro中进行name的修改。此处不进行修改。

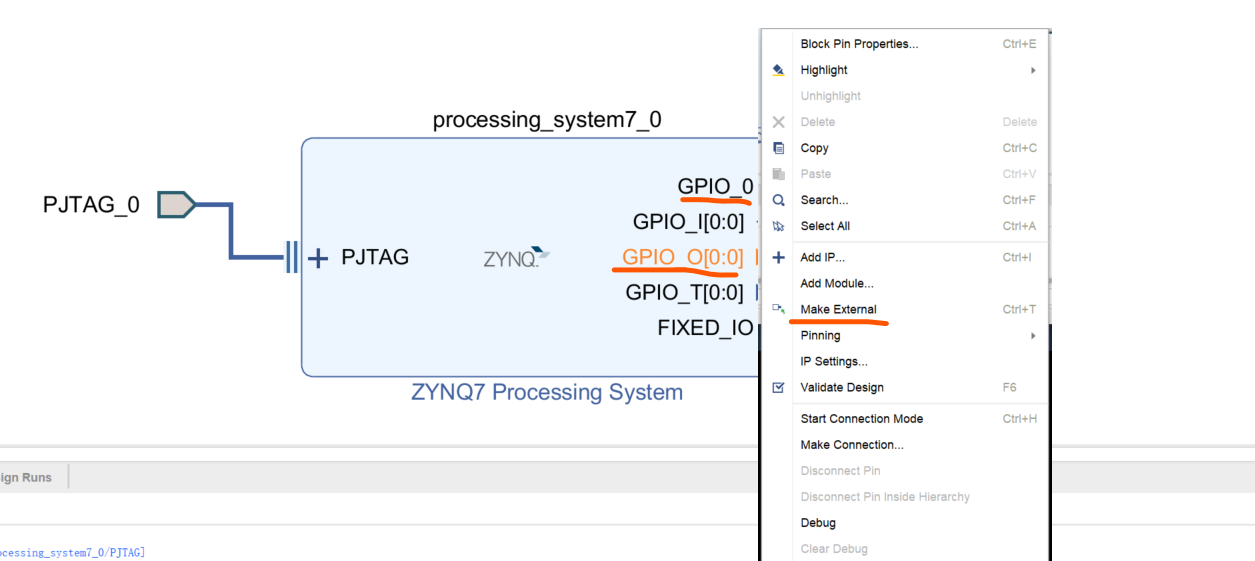

单击processing_system7_0中的GPIO_0管脚后面的+,展开GPIO_0管脚,此处我们只需要输出功能,所以单击GPIO_O[0:0],同样右击选择Make External。

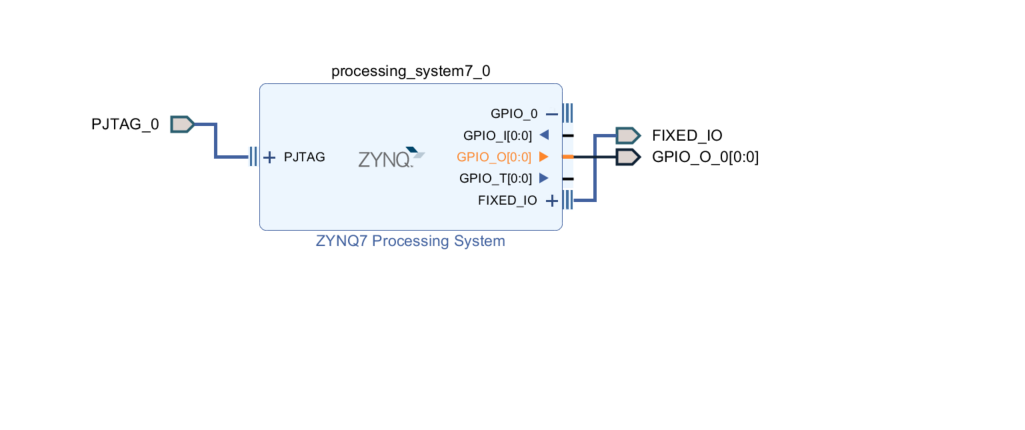

可以看到引出GPIO_O_0[0:0]管脚。改名方式同上文PJTAG,此处仍使用默认名称。

-

至此,CPU配置完成。

-

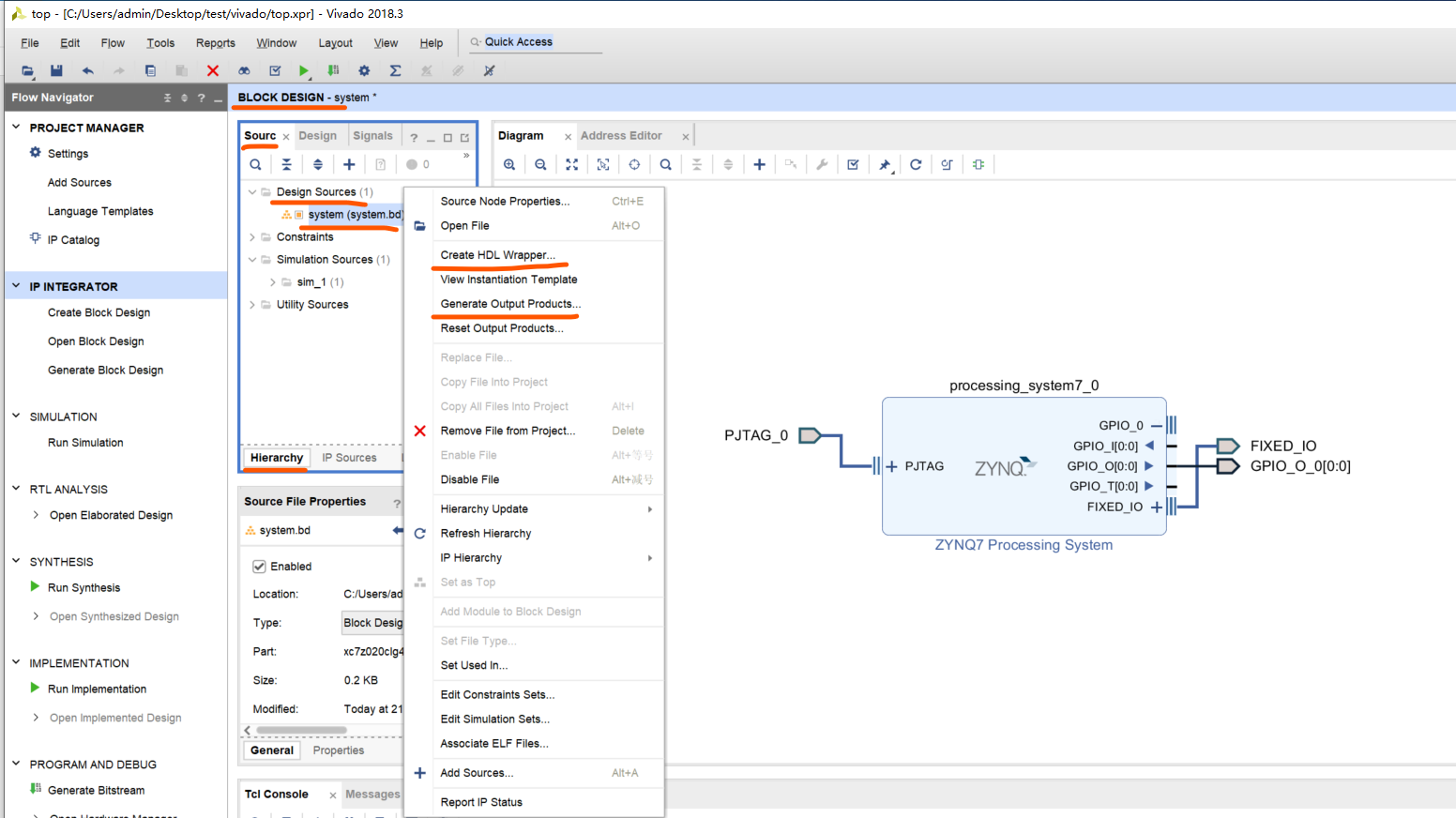

Block Design中选择Sources -> Hierarchy,右击Design Sources中的system。先选择Generate Output Products,进行编译。运行完成后,再选择Create HDL Wrapper,使用Let Vivado manage Wrapper and auto-update模式,生成system_wrapper.v。

-

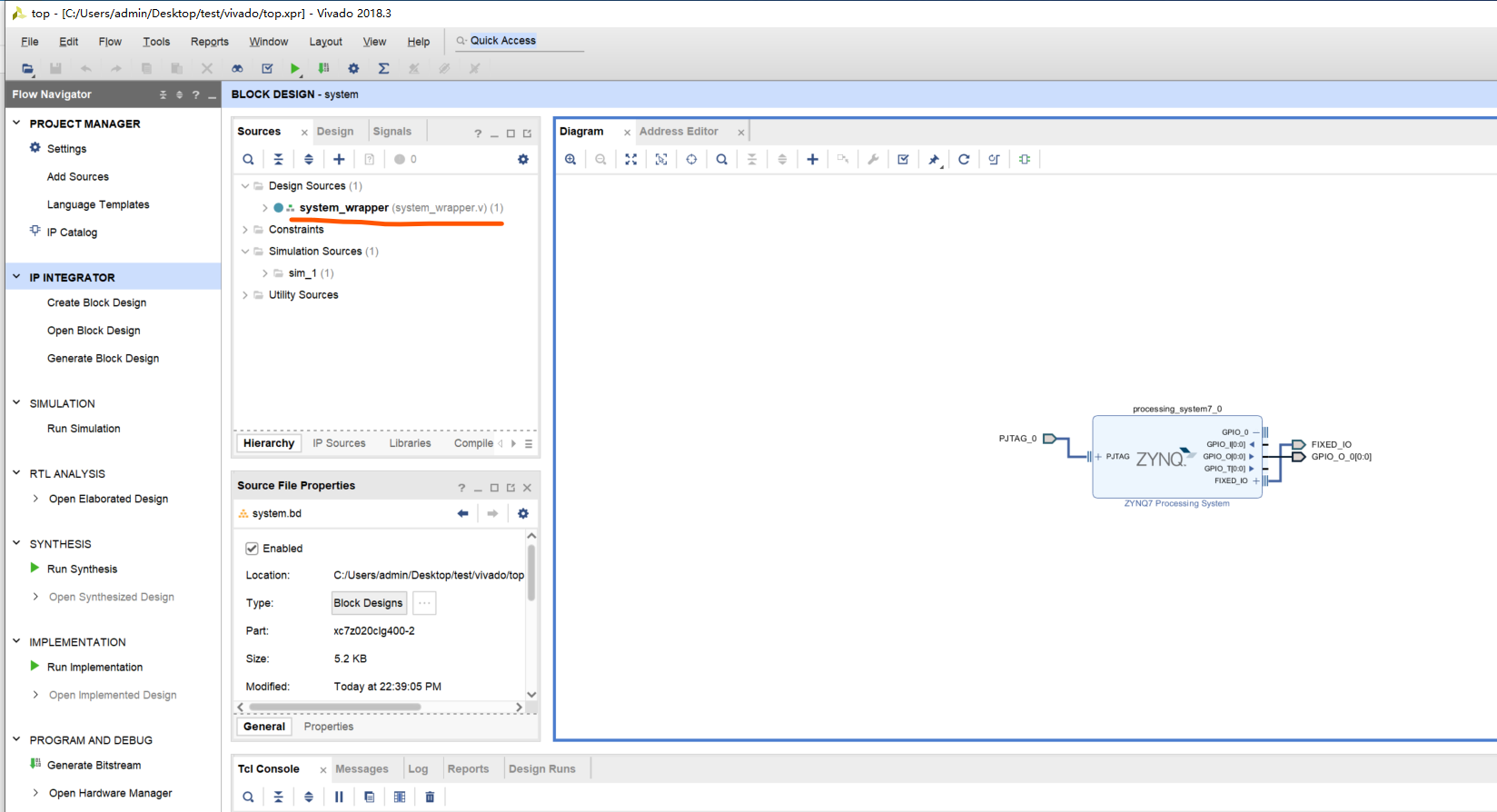

最终如下图所示。

-

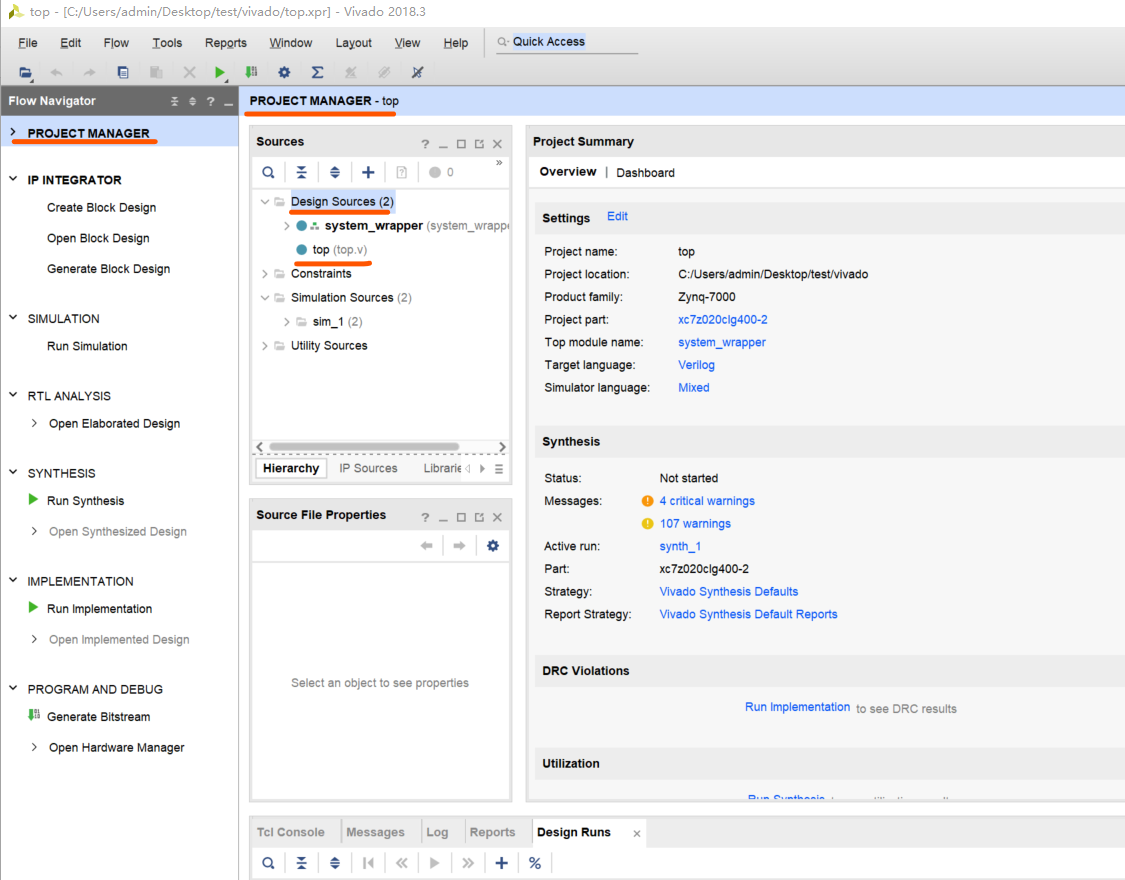

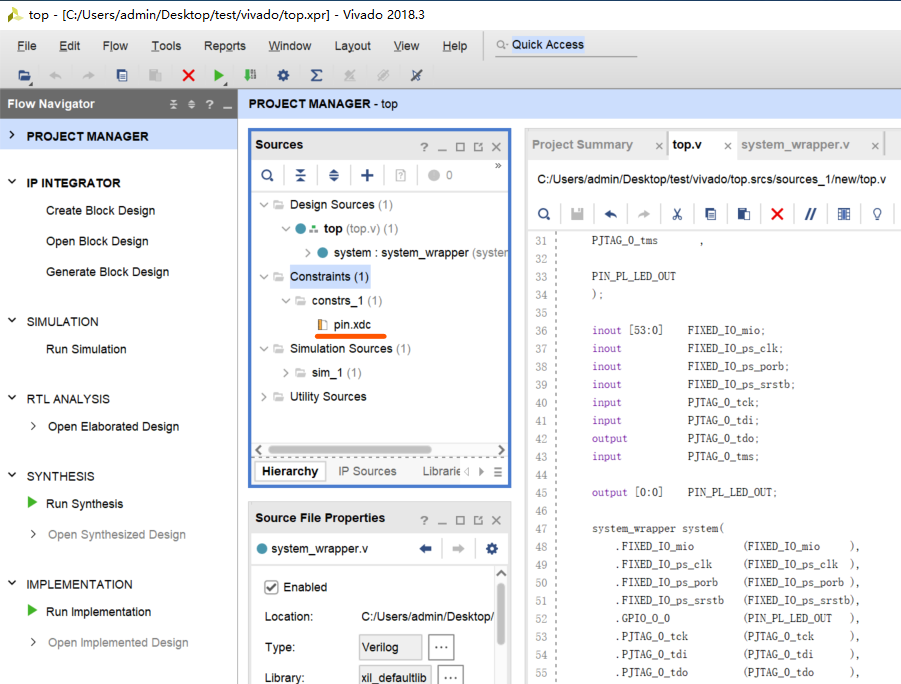

双击左侧Flow Navigator中的PROJECT MANAGER,在PROJECT MANAGER->Design Sources中新建top.v文件。

-

top.v中编写如下代码。

module top( FIXED_IO_mio , FIXED_IO_ps_clk , FIXED_IO_ps_porb , FIXED_IO_ps_srstb , PJTAG_0_tck , PJTAG_0_tdi , PJTAG_0_tdo , PJTAG_0_tms , PIN_PL_LED_OUT ); inout [53:0] FIXED_IO_mio; inout FIXED_IO_ps_clk; inout FIXED_IO_ps_porb; inout FIXED_IO_ps_srstb; input PJTAG_0_tck; input PJTAG_0_tdi; output PJTAG_0_tdo; input PJTAG_0_tms; output [0:0] PIN_PL_LED_OUT; system_wrapper system( .FIXED_IO_mio (FIXED_IO_mio ), .FIXED_IO_ps_clk (FIXED_IO_ps_clk ), .FIXED_IO_ps_porb (FIXED_IO_ps_porb ), .FIXED_IO_ps_srstb (FIXED_IO_ps_srstb), .GPIO_O_0 (PIN_PL_LED_OUT ), .PJTAG_0_tck (PJTAG_0_tck ), .PJTAG_0_tdi (PJTAG_0_tdi ), .PJTAG_0_tdo (PJTAG_0_tdo ), .PJTAG_0_tms (PJTAG_0_tms ) ); endmodule -

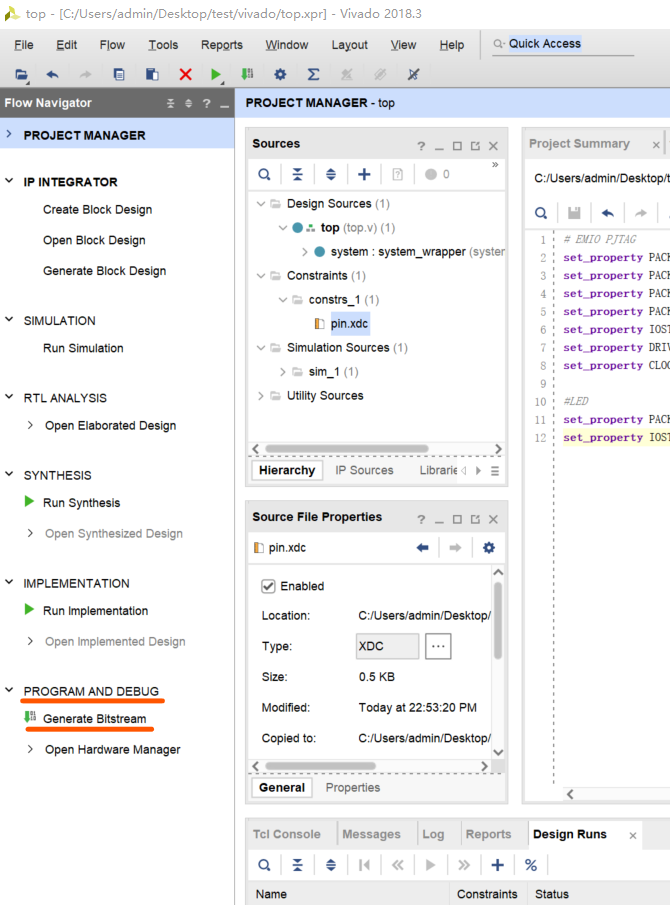

PROJECT MANAGER -> Constraints中新增pin.xdc文件。

-

pin.xdc中编写如下脚本。

# EMIO PJTAG set_property PACKAGE_PIN R16 [get_ports PJTAG_0_tck] set_property PACKAGE_PIN V18 [get_ports PJTAG_0_tdi] set_property PACKAGE_PIN V17 [get_ports PJTAG_0_tdo] set_property PACKAGE_PIN R17 [get_ports PJTAG_0_tms] set_property IOSTANDARD LVCMOS33 [get_ports PJTAG_0_*] set_property DRIVE 4 [get_ports {PJTAG_0_tdo}] set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets "PJTAG_0_tck"] #LED set_property PACKAGE_PIN V7 [get_ports {PIN_PL_LED_OUT[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {PIN_PL_LED_OUT[0]}] -

Flow Navigator中选择PROGRAM AND DEBUG -> Generate Bitstream,生成bit。

-

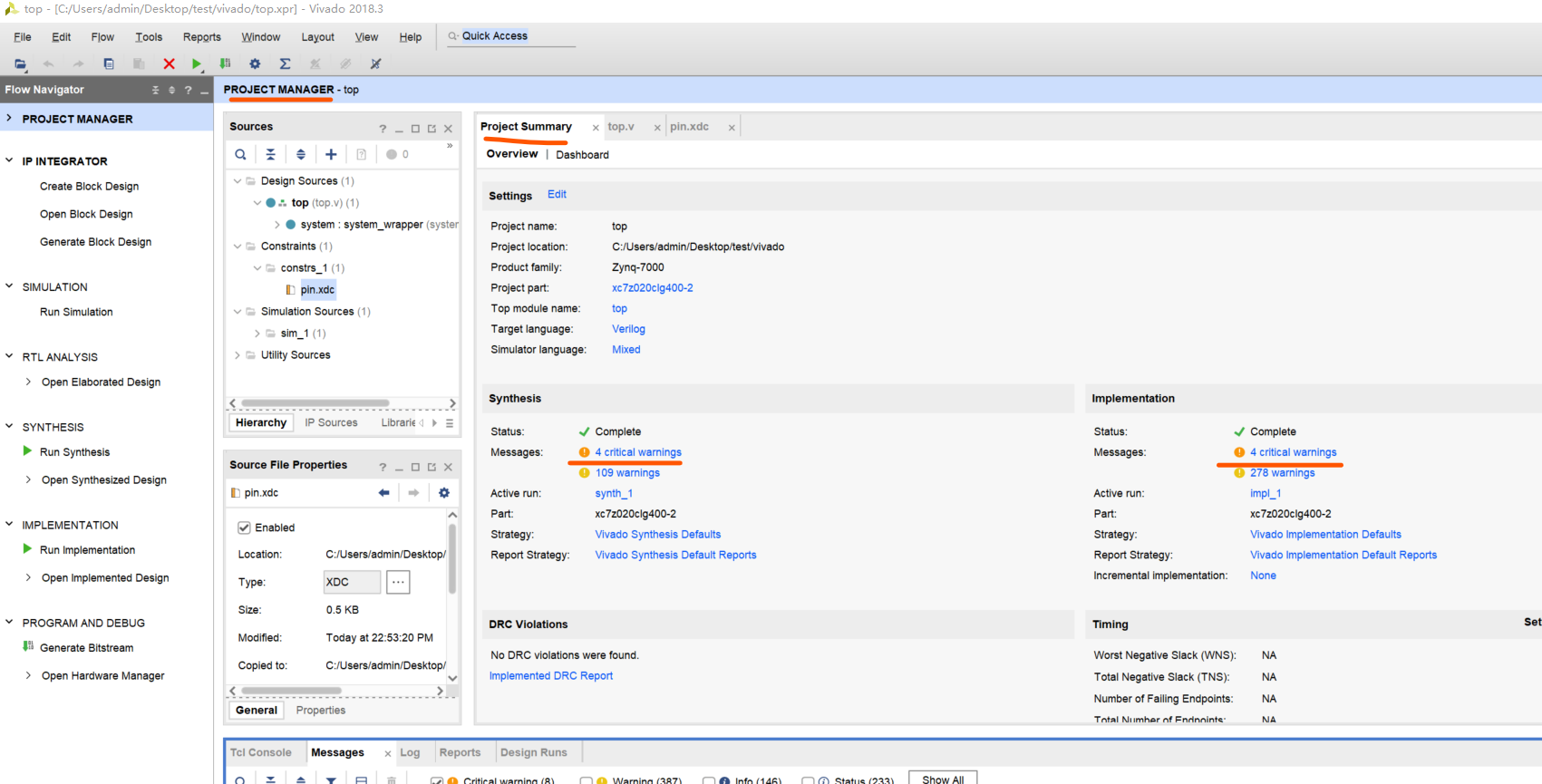

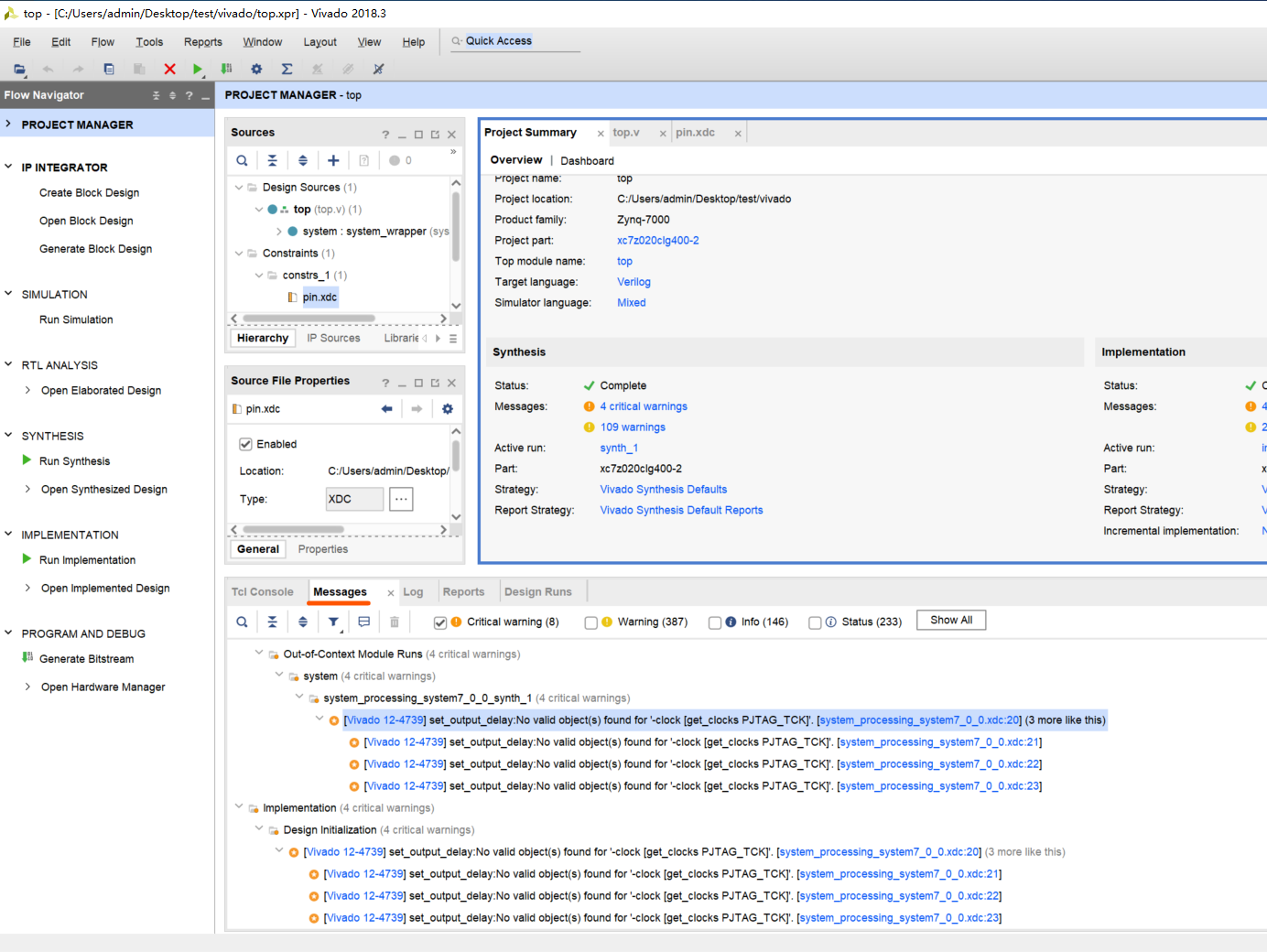

生成bit完成后,打开PROJECT MANAGER -> Project Summary,如下图。

可以看到Synthesis和Implementation各有4条严重警告,查询下方的Messages,可知严重警告均针对PJTAG_TCK信号。因pin.xdc中已对PJTAG_0_tck进行CLOCK_DEDICATED_ROUTE属性进行FALSE处理,但由于XDC文件优先级原因,导致产生警告的system_processing_system7_0_0.xdc文件先于pin.xdc文件编译,导致出现该严重警告。此严重警告不影响使用,故此处不再处理。

- 至此,VIVADO部分的工作完成。下面介绍Procise部分。

-

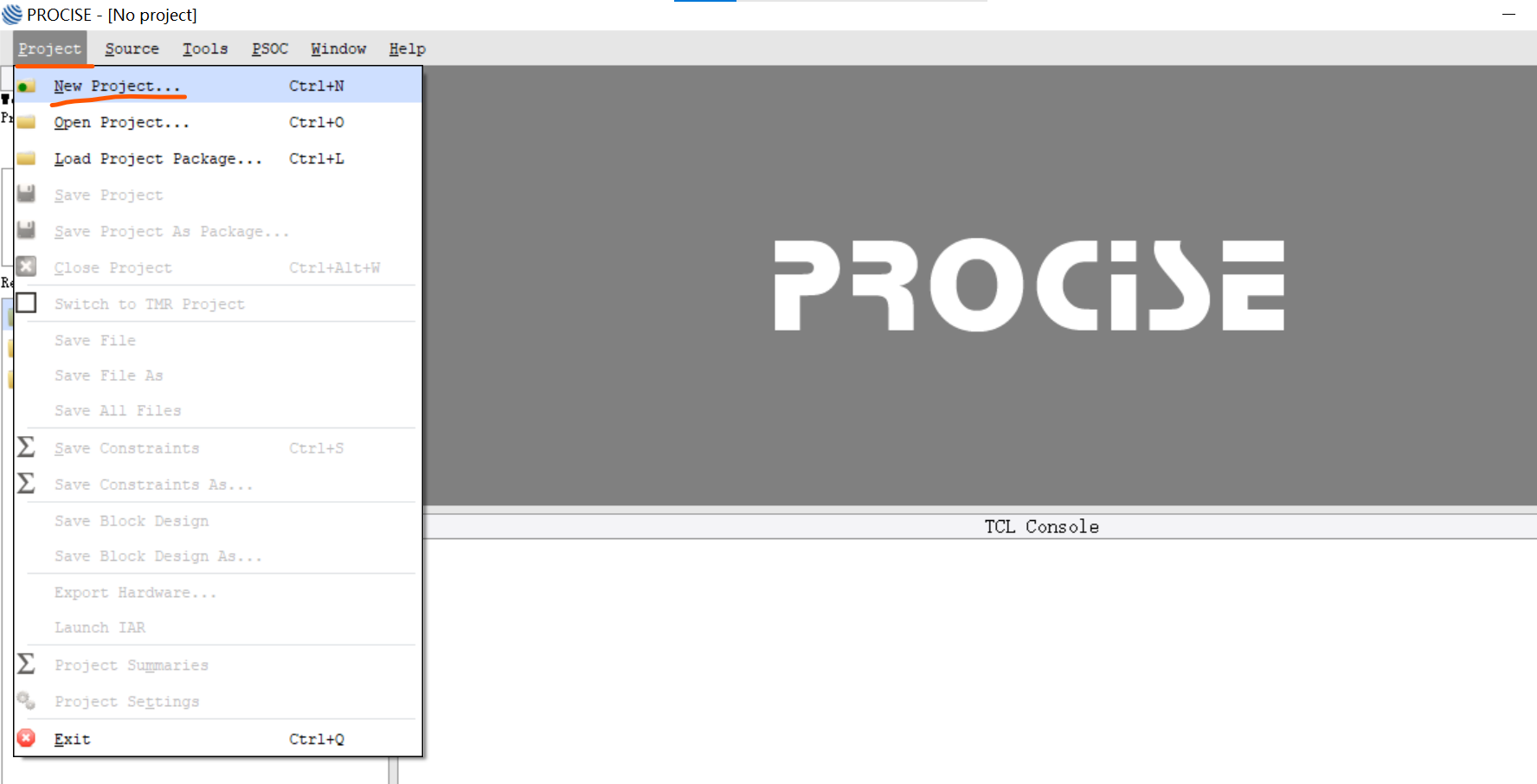

打开Procise软件,Project -> New Project,进行工程新建。

-

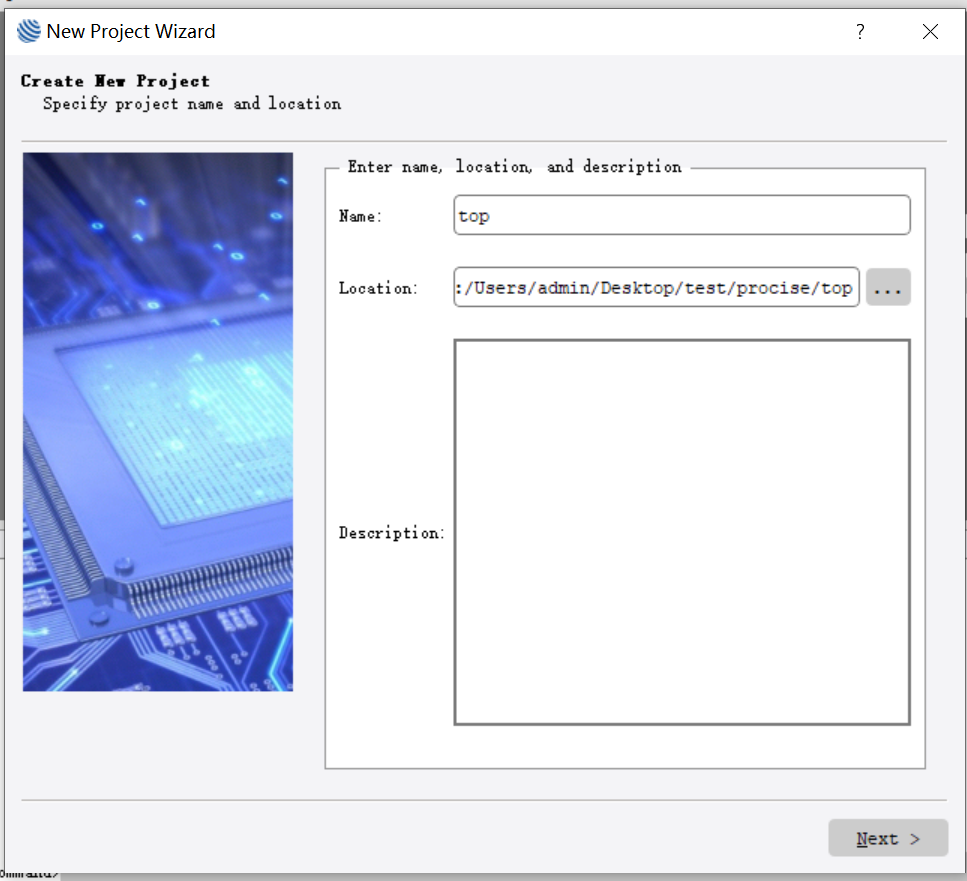

工程名称同VIVADO,设置为top。存放地址设置在本文开头新建的procise文件夹。

-

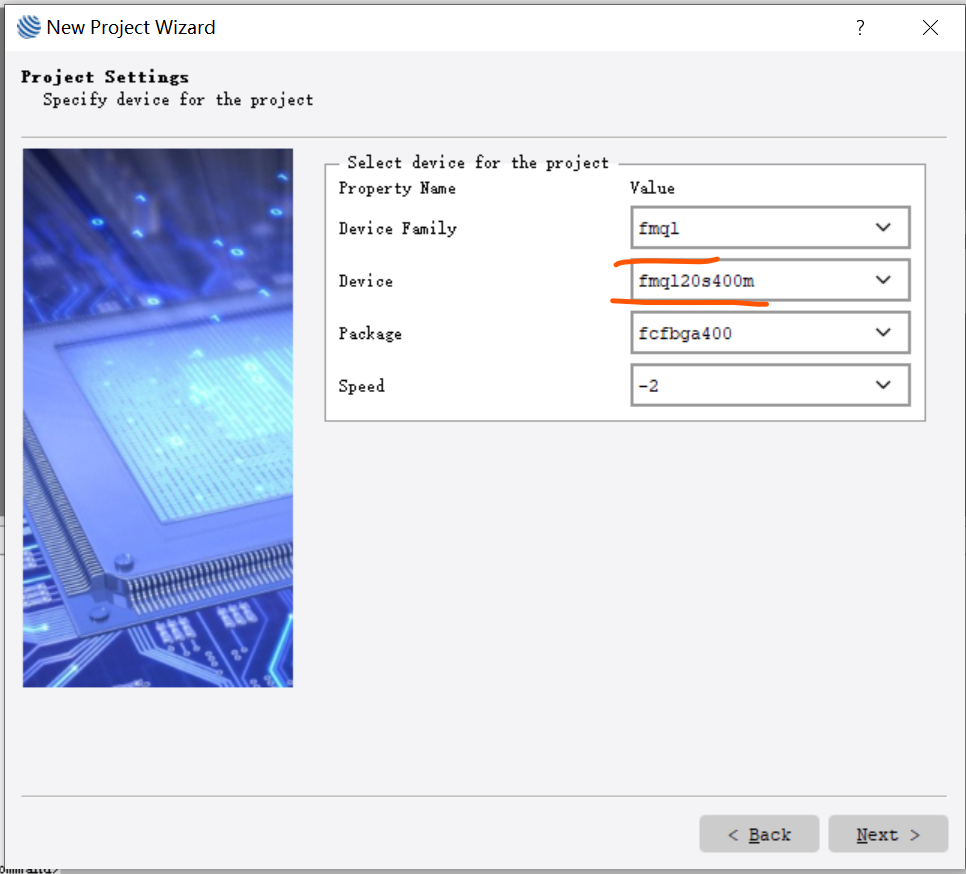

器件配置为FMQL20S400M。

- 剩余均选择默认配置,完成工程新建。

-

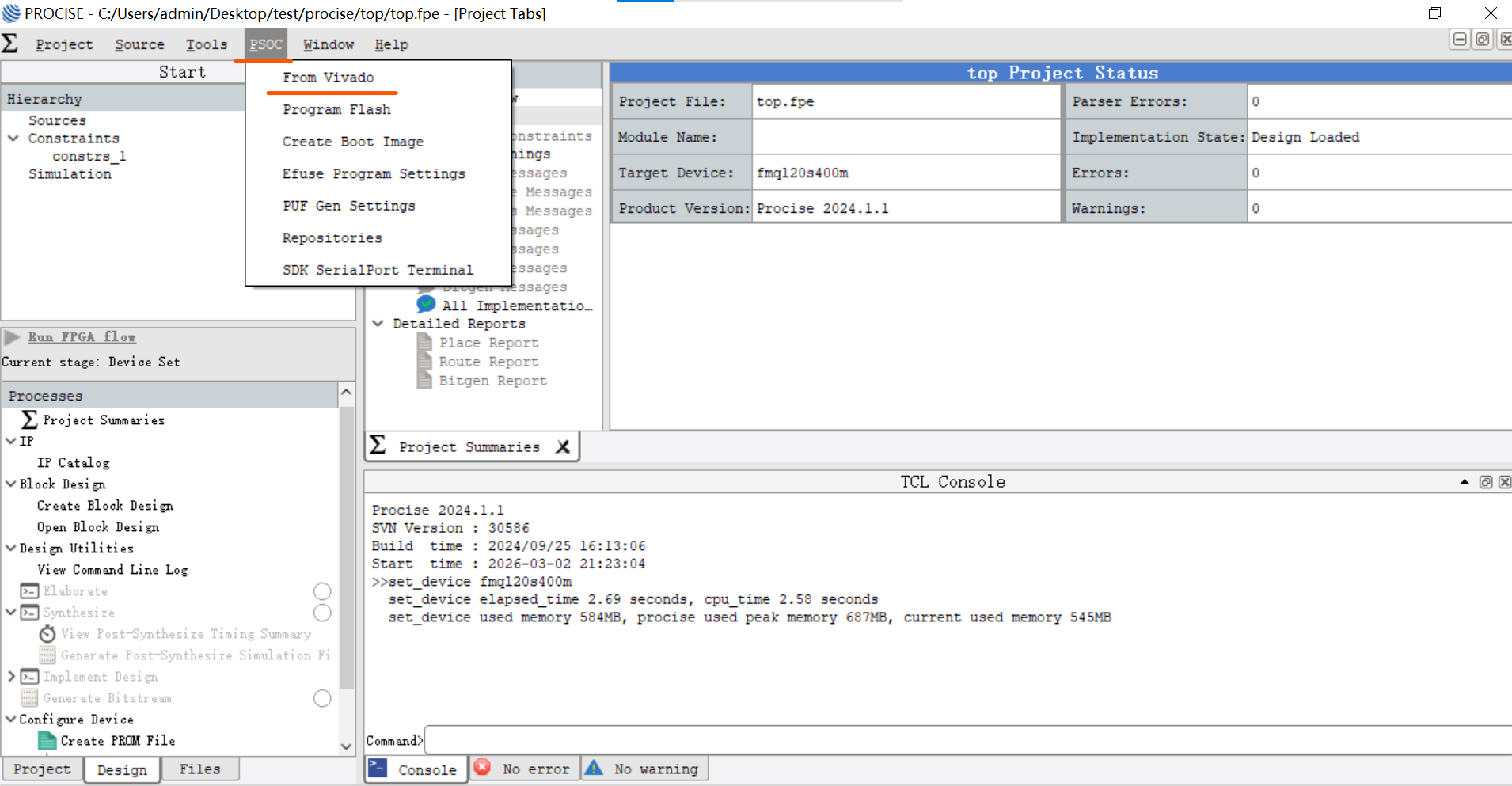

选择PSOC -> From Vivado,导入VIVADO工程。

-

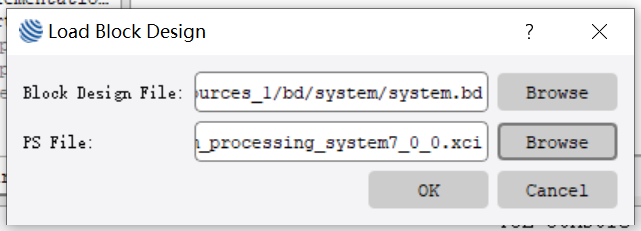

Block Design File位置填写VIVADO中生成的system.bd文件;PS File位置填写VIVADO中生成的CPU 配置文件。

Block Design文件(*.bd)的路径一般为:

{prj_name} \ {prj_name}.srcs \ sources_1 \ bd \ {bd_name} \ {bd_name}.bd

PS的配置文件(*.xci)的路径一般为:

{prj_name} \ {prj_name}.srcs \ sources_1 \ bd \ {bd_name} \ ip \ {bd_name}_processing_system7_0_0 \ {bd_name}_processing_system7_0_0.xci

-

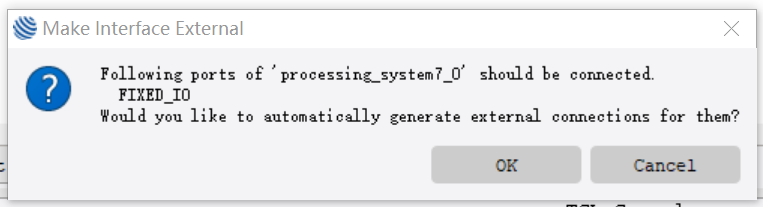

PROCISE导入VIVADO工程过程中会弹出如下对话框,选择OK即可。

-

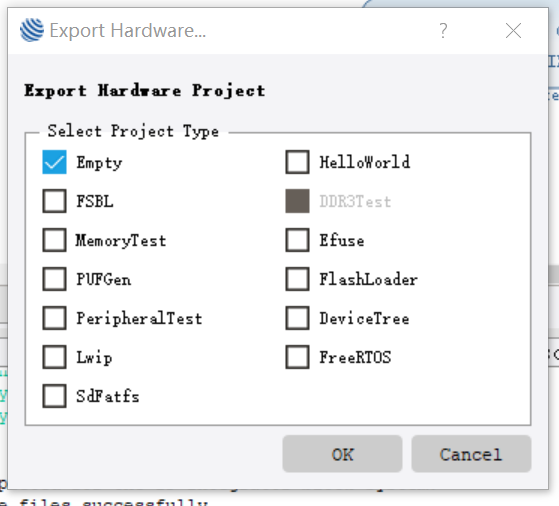

导入的最后一步,会弹出工程模板选择界面。这里默认勾选Empty。其余工程未来可根据实际开发需求选择即可。

-

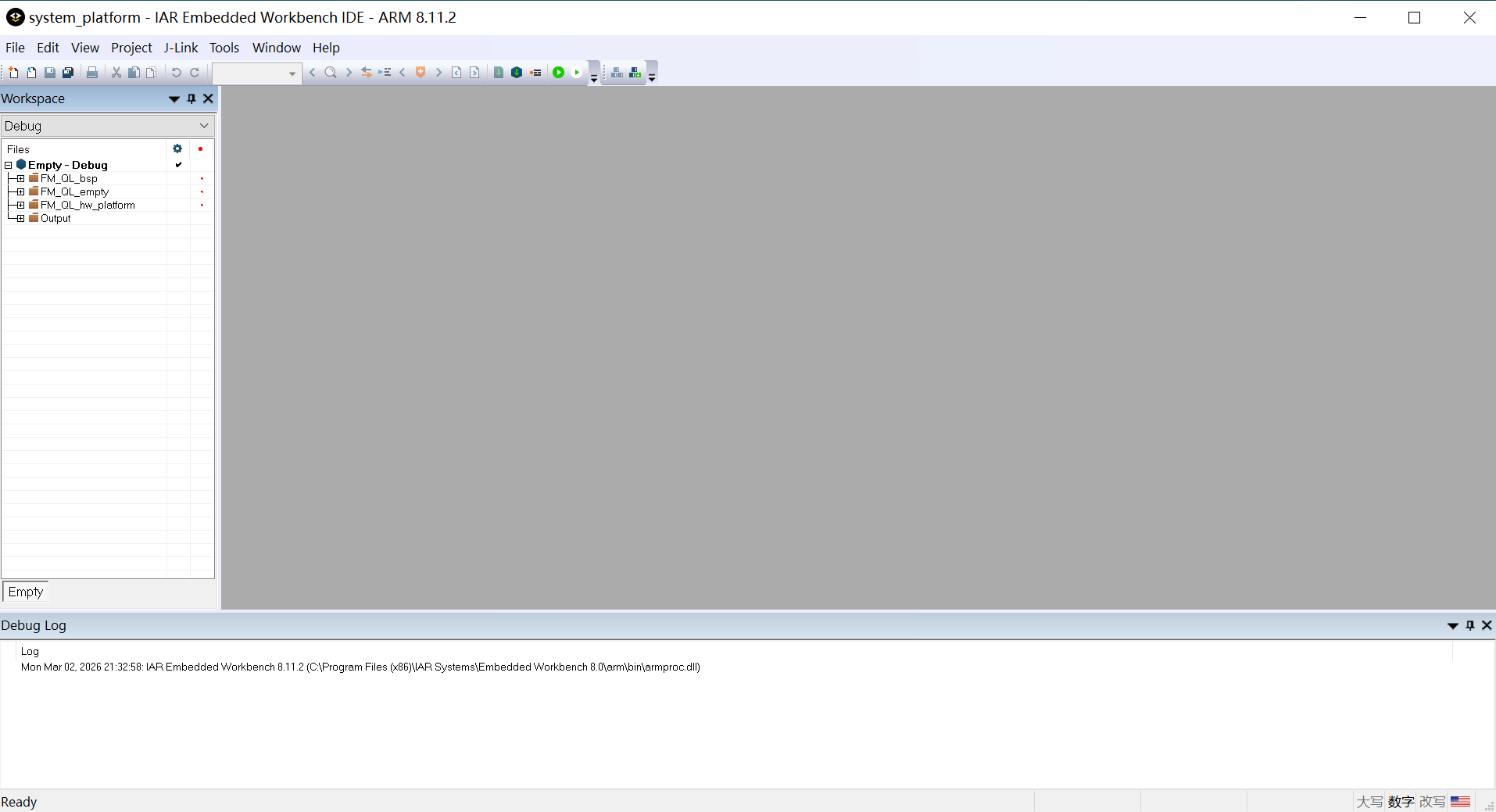

之后PROCISE会自动启动IAR。

-

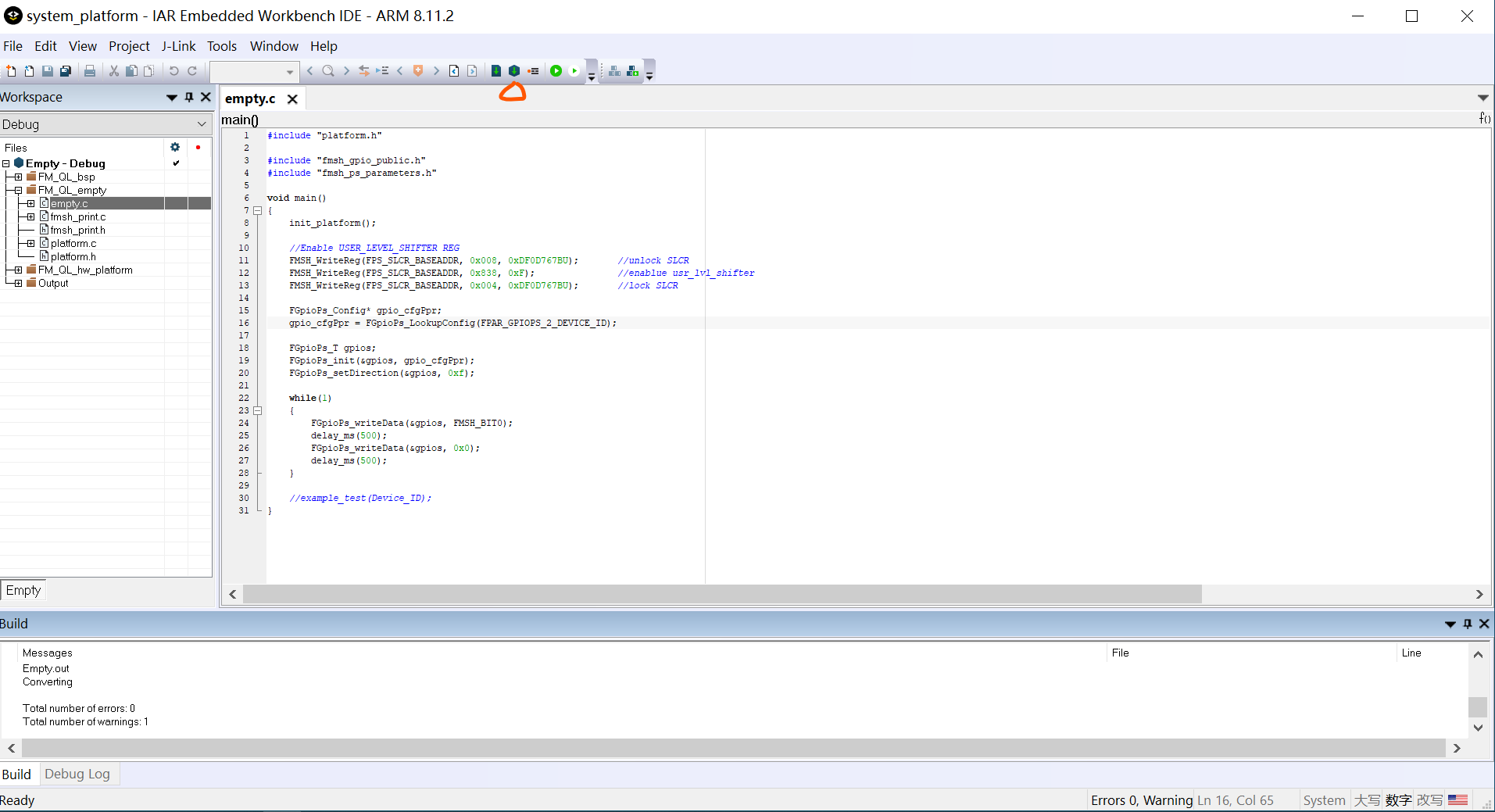

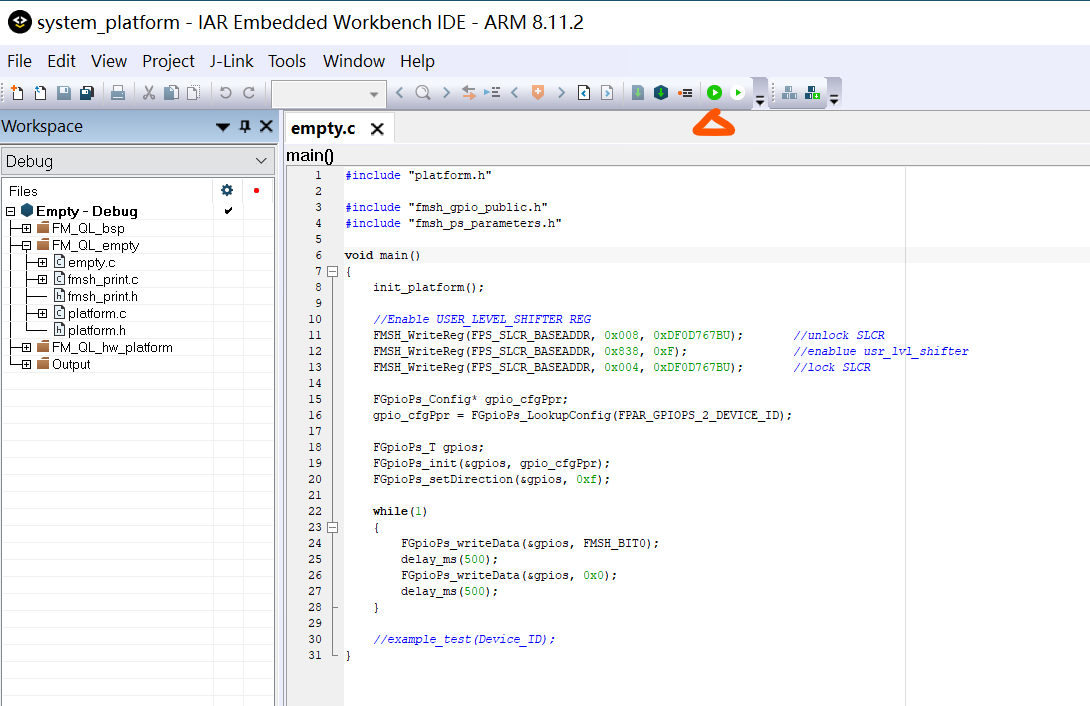

选择Workspace中的 FM_QL_empty,编辑empty.c文件。

#include "platform.h" #include "fmsh_gpio_public.h" #include "fmsh_ps_parameters.h" void main() { init_platform(); //Enable USER_LEVEL_SHIFTER REG FMSH_WriteReg(FPS_SLCR_BASEADDR, 0x008, 0xDF0D767BU); //unlock SLCR FMSH_WriteReg(FPS_SLCR_BASEADDR, 0x838, 0xF); //enablue usr_lvl_shifter FMSH_WriteReg(FPS_SLCR_BASEADDR, 0x004, 0xDF0D767BU); //lock SLCR FGpioPs_Config* gpio_cfgPpr; gpio_cfgPpr = FGpioPs_LookupConfig(FPAR_GPIOPS_2_DEVICE_ID); FGpioPs_T gpios; FGpioPs_init(&gpios, gpio_cfgPpr); FGpioPs_setDirection(&gpios, 0xf); while(1) { FGpioPs_writeData(&gpios, FMSH_BIT0); delay_ms(500); FGpioPs_writeData(&gpios, 0x0); delay_ms(500); } //example_test(Device_ID); } -

Make整个工程。最终0errors,1warnings。该warnings与fmsh_print.c文件相关,SendData功能声明但未使用。此处无影响,忽略该告警。

- 至此,PROCISE部分也完成设计(含IAR部分)。下面将程序下载到开发中进行调试。

- 开发板接好JLINK仿真器和JTAG下载器。上电之前将BOOT_SET拨码开关拨到[4:1]=1000位置。

-

给开发板上电,首先VIVADO烧写bit。完成后可以看到开发板中核心板的FPGA_DONE指示灯(红色,LED1)亮起。然后回到IAR,点击Download and Debug,完成程序下载后,进入调试模式。

调试模式中单击Go,让程序运行。可以看到开发板中核心板上挂在PL侧的蓝色指示灯LED2闪烁。

-

至此,PS和PL联合开发工程搭建完成,PL和PS可以单独调试。

注意:

- 首次上电烧写顺序必须先VIVADO,后IAR。因为VIVADO烧写后才能将PS侧的JTAG通过EMIO给引出供JLINK仿真器调试使用。

- 调试过程中,PS和PL均可单独调试、烧写。

如果这篇文章对您有帮助,欢迎打赏支持。

若需要工程原文件,请打赏1元后发送索取邮件到crazychip999@qq.com,记得附上打赏截图。